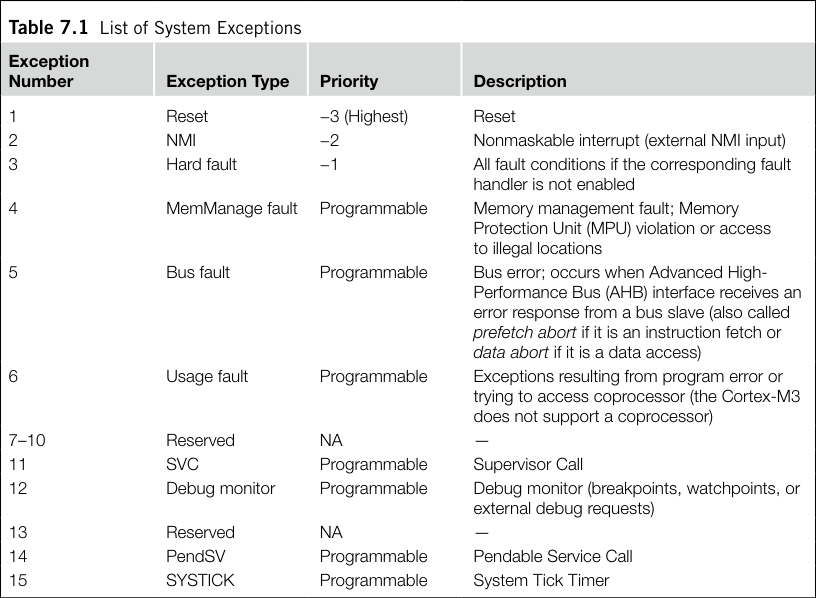

1. 예외 유형

예외는 시스템 예외의 경우 1-15번, 외부 인터럽트 입력의 경우 16번 이상입니다.

대부분의 예외에는 프로그래밍 가능한 우선 순위가 있으며 일부는 고정된 우선 순위를 가집니다.

Cortex-M3 칩은 서로 다른 수의 외부 인터럽트 입력(1에서 240까지)을 가질 수 있으며 서로 다른

우선 순위 수준의 수입니다.

예외 유형 1-15는 시스템 예외입니다(예외 유형 0은 없음).

유형 16 이상의 예외는 외부 인터럽트 입력입니다.

현재 실행 중인 예외의 값은 특수 레지스터 인터럽트 프로그램으로 표시됩니다.

상태 레지스터(IPSR) 또는 중첩 벡터 인터럽트 컨트롤러(NVIC)의 인터럽트 컨트롤러에서.

상태 레지스터(VECACTIVE 필드).

활성화된 예외가 발생했지만 즉시 실행할 수 없는 경우(예:

우선 인터럽트 서비스 루틴이 실행 중이거나 인터럽트 마스크 레지스터가 설정된 경우) 실행됩니다(제외).

일부 오류 예외). 이는 레지스터(“보류 중” 상태)에 예외 요청이 포함되어 있음을 의미합니다.

예외가 실행될 수 있을 때까지.

2.우선순위 정의

예외를 수행할 수 있는지 여부와 시기는 Cortex-M3에서 우선 순위를 통해 영향을 받을 수 있습니다.

예외. 우선 순위가 높은 예외(우선 순위 수준에서 작은 숫자)는 우선 순위가 낮은 예외를 선점할 수 있습니다.

(우선순위 수준에서 더 큰 숫자) 예외; 이것은 중첩된 예외/인터럽트 시나리오입니다.

일부 예외(재설정, NMI 및 하드 폴트)에는 고정된 우선 순위 수준이 있습니다. 그들은 음수입니다

다른 예외보다 우선 순위가 높음을 나타냅니다.

Cortex-M3는 3개의 고정된 최우선 순위 평면과 최대 256개의 프로그래밍 가능 평면을 지원합니다.

우선 순위(최대 128개의 선점 수준). 그러나 대부분의 Cortex-M3 칩은

지원되는 수준 – 예: 8, 16, 32 등. Cortex-M3 칩이나 SoC가 개발되면

디자이너는 필요한 레벨 수를 얻기 위해 사용자 정의할 수 있습니다. 이 레벨 감소는

우선 순위 구성 레지스터의 최하위 비트(LSB) 부분을 제거하여 구현됩니다.

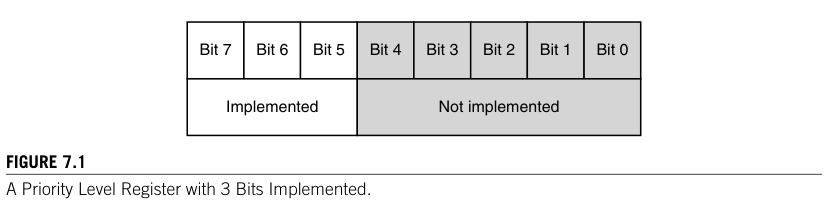

설계에서 우선순위 레벨의 3비트만 구현하면 우선순위 레벨 구성 레지스터가 좋아 보입니다.

그림 7.1과 같이.

비트 4 ~ 비트 0은 구현되지 않았으므로 항상 0으로 읽히고 이 비트에 대한 쓰기가 수행됩니다.

무시하십시오. 이 설정을 통해 가능한 우선 순위 수준은 0x00(높은 우선 순위), 0x20, 0x40, 0x60,

0x80, 0xA0, 0xC0 및 0xE0(최저).

3. 벡터 테이블

4. 인터럽트 입력 및 보류 중인 동작

5. 오류 예외

6. 감독자 호출 및 보류 중인 서비스 호출